### HY3842/43/44/45

#### DESCRIPTION

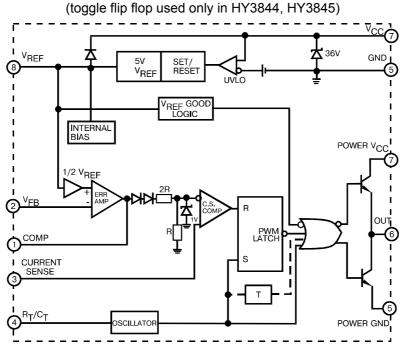

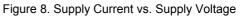

The HY3842D-N/3843D-N/3844D-N/3845D-N, are fixed frequency

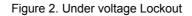

current mode PWM controller. They are specially designed for OFF-Line and DC to DC converter applications with a minimal external components. Internally implemented circuits include a trimmed oscillator for precise duty cycle control, a temperature compensated reference, high gain error amplifier, current sensing comparator, and a high current totem pole output ideally suited for driving a power MOSFET. Protection circuitry

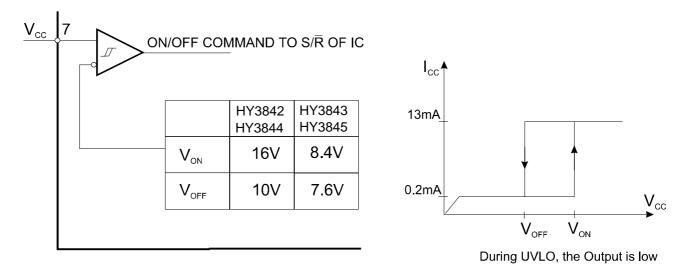

includes built under voltage lockout and current limiting. The HY3842D-N, HY3844D-N, have UVLO thresholds of 16 V (on) and 10 V (off). The corresponding thresholds for the HY3843D-N/3845D-N are 8.4V (on) and 7.6V (off). The HY3842D-N, HY3843D-N, can operate within 100% duty cycle. The HY3844D-N, HY3845D-N, can operate within 50% duty cycle.

The HY384XD-N have Start-Up Current 0.17mA (typ).

#### **FEATURES**

- Low Start-Up and Operating Current

- High Current Totem Pole Output

- Under voltage Lockout With Hysteresis

- Operating Frequency Up To 500KHz

### BLOCK DIAGRAM

#### **Absolute Maximum Ratings**

| Characteristic                                        | Symbol                  | Value       | Unit |

|-------------------------------------------------------|-------------------------|-------------|------|

| Supply Voltage (low impedance source)                 | V <sub>cc</sub>         | 30          | V    |

| Output Current                                        | lo                      | ±1          | A    |

| Input Voltage (Analog Inputs pins 2,3)                | VI                      | -0.3 to 5.5 | V    |

| Error Amp Output Sink Current                         | I <sub>SINK (E.A)</sub> | 10          | mA   |

| Power Dissipation (T <sub>A</sub> =25 <sup>0</sup> C) | Po                      | 1           | W    |

| Storage Temperature Range                             | Tstg                    | -65 to150   | °C   |

| Lead Temperature (soldering 5 sec.)                   | TL                      | 260         | °C   |

## HY3842/43/44/45

### Electrical characteristics (\* $V_{CC}$ =15V, R<sub>T</sub>=10k $\Omega$ , C<sub>T</sub>=3.3nF, T<sub>A</sub>=0<sup>o</sup>C to +70<sup>o</sup>C, unless otherwise specified)

| Characteristics               | Symbol                     | Test Condition                                       | Min  | Тур     | Max  | Unit |

|-------------------------------|----------------------------|------------------------------------------------------|------|---------|------|------|

| Reference Section             |                            | •                                                    |      | •       | •    |      |

| Reference Output Voltage      | V <sub>REF</sub>           | $T_{J} = 25^{\circ}C, I_{REF} = 1 \text{ mA}$        | 4.9  | 5.0     | 5.1  | V    |

| Line Regulation               | $\Delta V_{REF}$           | $12V \le V_{CC} \le 25 V$                            |      | 6.0     | 20   | mV   |

| Load Regulation               | $\Delta V_{REF}$           | $1 \text{ mA} \leq I_{\text{REF}} \leq 20 \text{mA}$ |      | 6.0     | 25   |      |

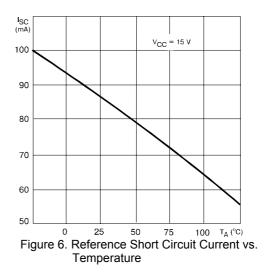

| Short Circuit Output Current  | I <sub>SC</sub>            | T <sub>A</sub> = 25°C                                |      | -100    | -180 | mA   |

| Oscillator Section            |                            |                                                      |      |         |      |      |

| Oscillation Frequency         | f                          | T <sub>.1</sub> = 25°C                               | 47   | 52      | 57   | KHz  |

| Frequency Change with Voltage | $\Delta f / \Delta V_{CC}$ | $12V \le V_{CC} \le 25 V$                            |      | 0.05    | 1.0  | %    |

| Oscillator Amplitude          | V <sub>(OSC)</sub>         | (peak to peak)                                       |      | 1.6     |      | V    |

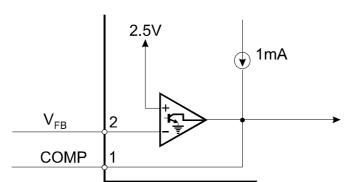

| Error Amplifier Section       | (000)                      |                                                      |      |         |      |      |

| Input Bias Current            | I <sub>BIAS</sub>          | V <sub>FB</sub> =3V                                  |      | -0.1    | -2   | μA   |

| Input Voltage                 | V <sub>I(E.A)</sub>        | V <sub>pin1</sub> = 2.5V                             | 2.42 | 2.5     | 2.58 | V    |

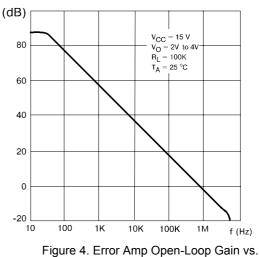

| Open Loop Voltage Gain        | A <sub>VOL</sub>           | $2V \le V_0 \le 4V$                                  | 65   | 90      |      | dB   |

| Unity Gain Bandwidth          | UGBW                       | T <sub>i</sub> =25 <sup>0</sup> C, Note 3            | 0.5  | 0.6     |      | MHz  |

| Power Supply Rejection Ratio  | PSRR                       | $12V \le V_{CC} \le 25 V$                            | 60   | 70      |      | dB   |

| Output Sink Current           | I <sub>SINK</sub>          | V <sub>pin2</sub> = 2.7V, V <sub>pin1</sub> = 1.1V   | 2    | 7       |      | mA   |

| Output Source Current         | ISOURCE                    | V <sub>pin2</sub> = 2.3V, V <sub>pin1</sub> = 5V     | -0.5 | -1.0    |      | mA   |

| High Output Voltage           | V <sub>OH</sub>            | $V_{pin2}$ = 2.3V, $R_L$ = 15K $\Omega$ to GND       | 5.0  | 6.0     |      | .,   |

| Low Output Voltage            | V <sub>OL</sub>            | $V_{pin2} = 2.7V, R_L = 15K\Omega$ to PIN 8          |      | 0.8     | 1.1  | V    |

| Current Sense Section         |                            |                                                      |      |         |      |      |

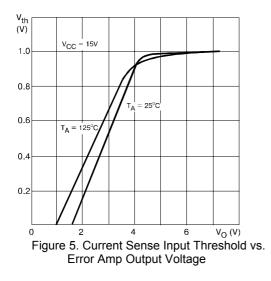

| Gain                          | Gv                         | (Note 1 & 2)                                         | 2.85 | 3.0     | 3.15 | V/V  |

| Maximum Input Signal          | V <sub>I(MAX)</sub>        | $V_{pin1} = 5V$ (Note1)                              | 0.9  | 1.0     | 1.1  | V    |

| Supply Voltage Rejection      | SVR                        | $12V \le V_{CC} \le 25 V$ (Note 1)                   |      | 70      |      | dB   |

| Input Bias Current            | I <sub>BIAS</sub>          | $V_{pin3} = 3V$                                      |      | -3.0    | -10  | μA   |

| Output Section                |                            | -                                                    |      |         |      |      |

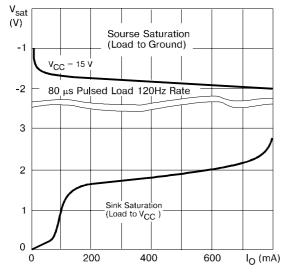

| Low Output Voltage            | V <sub>OL</sub>            | I <sub>SINK</sub> = 20 mA                            |      | 0.08    | 0.4  |      |

|                               |                            | I <sub>SINK</sub> = 200 mA                           |      | 1.4     | 2.2  | v    |

| High Output Voltage           | V <sub>OH</sub>            | I <sub>SINK</sub> = 20 mA                            | 13   | 13.5    |      | v    |

|                               |                            | I <sub>SINK</sub> = 200 mA                           | 12   | 13.0    |      |      |

| Rise Time                     | t <sub>R</sub>             | $T_J = 25^{\circ}C, C_L = 1nF$ (Note 3)              |      | 45      | 150  | nS   |

| Fall Time                     | t <sub>F</sub>             | $T_J = 25^{\circ}C, C_L = 1nF$ (Note 3)              |      | 35      | 150  | 113  |

| Undervoltage Lockout Section  |                            |                                                      |      |         |      |      |

| Start Theshold                | V <sub>TH(ST)</sub>        | HY3842D-N/44D-N                                      | 14.5 | 16.0    | 17.5 | v    |

|                               |                            | HY3843D-N/45D-N                                      | 7.8  | 8.4     | 9.0  | v    |

| Min. Operating Voltage        | $V_{\text{OPR(min)}}$      | HY3842D-N/44D-N                                      | 8.5  | 10      | 11.5 | v    |

| (After Turn On)               |                            | HY3843D-N/45D-N                                      | 7.0  | 7.6     | 8.2  | v    |

| PWM Section                   | -i                         |                                                      |      | i       |      | i    |

| Max. Duty Cycle               | D <sub>(MAX)</sub>         | HY3842D-N/43D-N                                      | 95   | 97      | 100  |      |

|                               |                            | HY3844D-N/45D-N                                      | 47   | 48      | 50   | %    |

| Min. Duty Cycle               | D <sub>(MAX)</sub>         |                                                      |      |         | 0    |      |

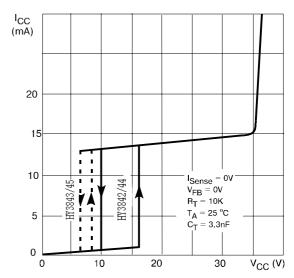

| Total Standby Current         |                            | 1                                                    |      | ı — — — | I    | 1    |

| Chart Lie Current             |                            | HY3843D-N, HY3845D-N                                 |      | 0.17    | 0.3  |      |

| Start-Up Current              | I <sub>ST</sub>            | HY3842D-N, HY3844D-N                                 |      | 0.17    | 0.3  | mA   |

| Operating Supply Current      | I <sub>CC (OPR)</sub>      | V <sub>pin3</sub> = V <sub>pin2</sub> = 0V           |      | 13      | 17   |      |

| Zener Voltage                 | V <sub>Z</sub>             | I <sub>CC</sub> =25 mA                               | 30   | 38      |      | V    |

\* Adjust V<sub>CC</sub> above the start threshold before setting it to 15V. Note 1: Parameter measured at trip point of latch with V<sub>pin2</sub>=0. Note 2: Gain defined as  $A=\Delta V_{pin1}/\Delta V_{pin3}$ ;  $0 \le V_{pin3} \le 0.8V$ . Note 3: These parameters, although guaranteed, are not 100% tested in production.

## HY3842/43/44/45

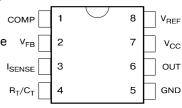

### **PIN FUNCTION**

| Ν | FUNCTION                       | DESCRIPTION                                                                                                                                     |  |  |

|---|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

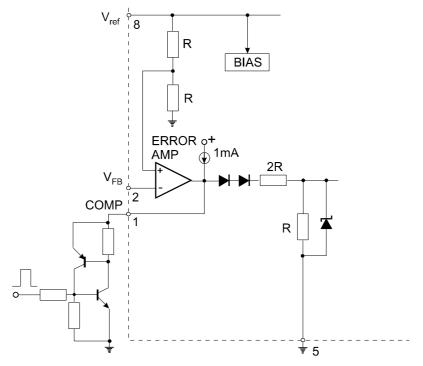

| 1 | COMP                           | This pin is the Error Amplifier output and is made for loop compensation.                                                                       |  |  |

| 2 | V <sub>FB</sub>                | This is the inverting input of the Error Amplifier. It is normally connected to the switching power supply output through a resistor divider.   |  |  |

| 3 | I <sub>SENSE</sub>             | A voltage proportional to inductor current is connected to this input. The PWM uses this information to terminate the output switch conduction. |  |  |

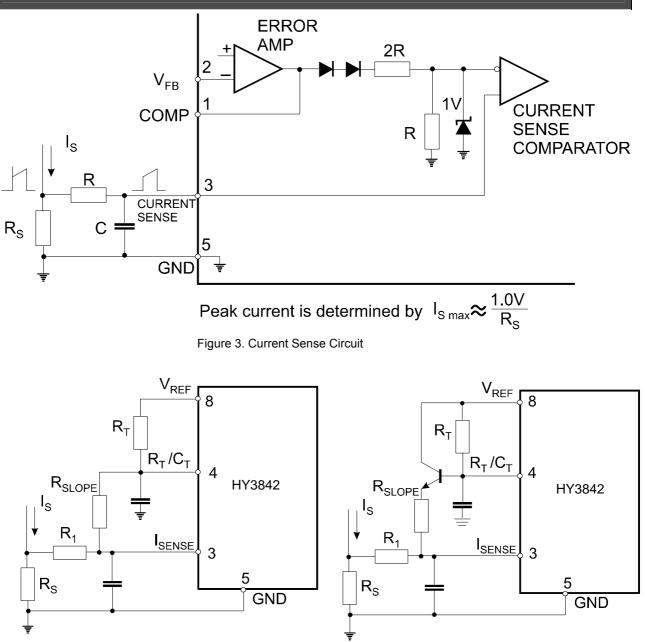

| 4 | R <sub>T</sub> /C <sub>T</sub> | The oscillator frequency and maximum Output duty cycle are programmed by connecting resistor $R_T$ to $V_{ref}$ and capacitor $C_T$ to ground.  |  |  |

| 5 | GROUND                         | This pin is the combined control circuitry and power ground.                                                                                    |  |  |

| 6 | OUTPUT                         | This output directly drives the gate of a power MOSFET. Peak currents up to 1A are sourced and sink by this pin.                                |  |  |

| 7 | V <sub>CC</sub>                | This pin is the positive supply of the integrated circuit.                                                                                      |  |  |

| 8 | V <sub>ref</sub>               | This is the reference output. It provides charging current for capacitor $C_T$ through resistor $R_T$ .                                         |  |  |

#### **APPLICATION INFORMATION**

HY3842/43/44/45

Figure 4. Slope Compensation Techniques

## HY3842/43/44/45

SCR must be selected for a holding current of less than 0.5mA. The simple two transistor circuit can be used in place of the SCR as shown.

Figure 5. Latched Shutdown

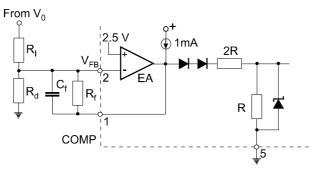

Error Amp compensation circuit for stabilizing any current-mode topology except for boost and flyback converters operating with continuous inductor current.

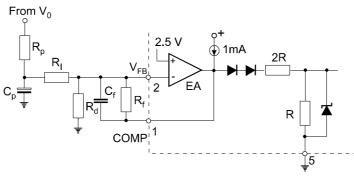

Error Amp compensation circuit for stabilizing current-mode boost and flyback topologies operating with continuous inductor current.

Figure 6. Error Amplifier Compensation

## HY3842/43/44/45

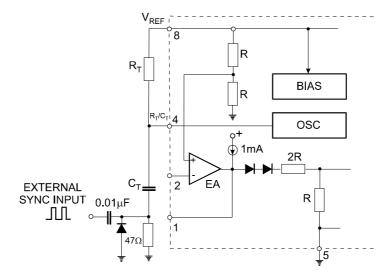

Figure 7. External Clock Synchronization

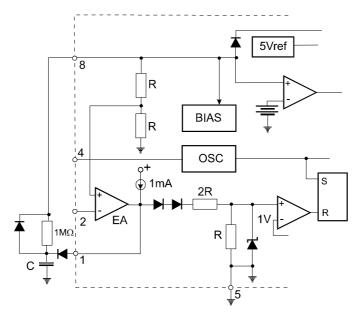

Figure 8. Soft-Start Circuit

### HY3842/43/44/45

### **TYPICAL PERFORMANCE CHARACTERISTICS**

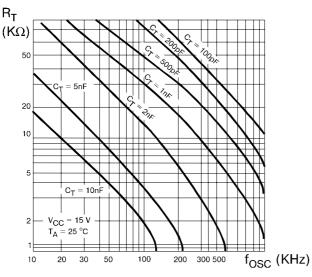

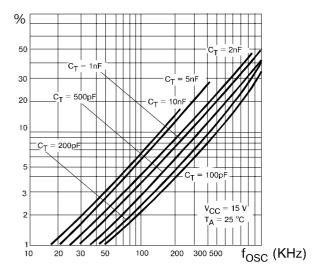

Figure 1. Timing Resistor vs. Oscillator Frequency

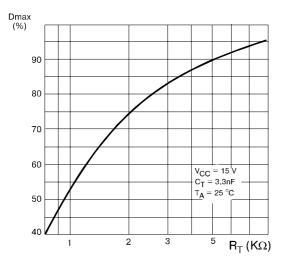

Figure 3. Maximum Output Duty Cycle vs. Timing Resistor (HY3842/43)

Frequency

### HY3842/43/44/45

Figure 9. Oscillator and Output Waveforms

## HY3842/43/44/45

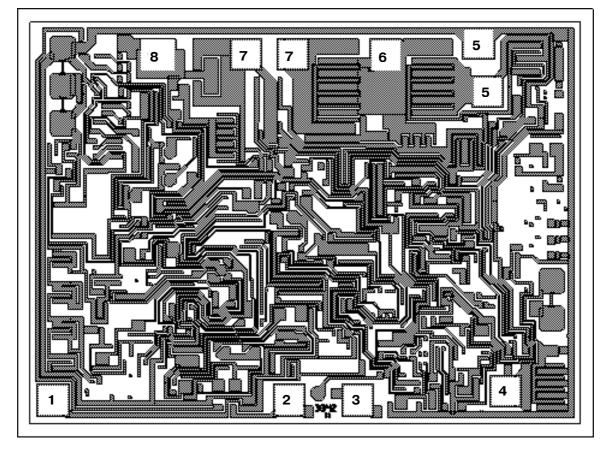

### PAD LOCATION

Chip size: 1.82 x 1.35 mm<sup>2</sup>

| Pad N  | Pad Name                       | Coordinates μm |      |  |

|--------|--------------------------------|----------------|------|--|

| T ad N |                                | X              | Y    |  |

| 1      | COMP                           | 114            | 115  |  |

| 2      | V <sub>FB</sub>                | 861            | 115  |  |

| 3      | I <sub>SENSE</sub>             | 1077           | 115  |  |

| 4      | R <sub>T</sub> /C <sub>T</sub> | 1545           | 143  |  |

| 5      | POWER GND                      | 1487           | 1090 |  |

| 5      | GND                            | 1459           | 1240 |  |

| 6      | OUT                            | 1167           | 1207 |  |

| 7      | POWER V <sub>CC</sub>          | 873            | 1207 |  |

| 7      | V <sub>CC</sub>                | 723            | 1207 |  |

| 8      | V <sub>REF</sub>               | 453            | 1207 |  |

### PAD LOCATION COORDINATES

The appearance complies with the requirements of the company standards.